### May 1999 File Number 3392.6

# Dual, 125MHz, Video Current Feedback Amplifier with Disable

intercil

The HA5022 is a dual version of the popular Intersil HA5020. It features wide bandwidth and high slew rate, and is optimized for video applications and gains between 1 and 10. It is a current feedback amplifier and thus yields less bandwidth degradation at high closed loop gains than voltage feedback amplifiers.

The low differential gain and phase, 0.1dB gain flatness, and ability to drive two back terminated  $75\Omega$  cables, make this amplifier ideal for demanding video applications.

The HA5022 also features a disable function that significantly reduces supply current while forcing the output to a true high impedance state. This functionality allows 2:1 video multiplexers to be implemented with a single IC.

The current feedback design allows the user to take advantage of the amplifier's bandwidth dependency on the feedback resistor. By reducing  $R_F$ , the bandwidth can be increased to compensate for decreases at higher closed loop gains or heavy output loads.

### Ordering Information

| PART NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C)       | PACKAGE    | PKG.<br>NO. |  |

|-------------|----------------------------------------|------------|-------------|--|

| HA5022IP    | -40 to 85                              | 16 Ld PDIP | E16.3       |  |

| HA5022IB    | -40 to 85                              | 16 Ld SOIC | M16.15      |  |

| HA5022EVAL  | High Speed Op Amp DIP Evaluation Board |            |             |  |

#### Features

- Dual Version of HA-5020

- Individual Output Enable/Disable

- Differential Gain ..... 0.03%

- Supply Current (per Amplifier) ..... 7.5mA

- Guaranteed Specifications at ±5V Supplies

### Applications

- Video Multiplexers; Video Switching and Routing

- Video Gain Block

- Video Distribution Amplifier/RGB Amplifier

- Flash A/D Driver

- Current to Voltage Converter

- Medical Imaging

- Radar and Imaging Systems

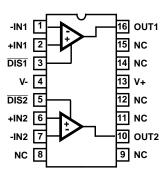

### Pinout

### **Absolute Maximum Ratings**

| Voltage Between V+ and V- Terminals                    |

|--------------------------------------------------------|

| DC Input Voltage (Note 3) ±V <sub>SUPPLY</sub>         |

| Differential Input Voltage10V                          |

| Output Current (Note 4) Short Circuit Protected        |

| ESD Rating (Note 3)                                    |

| Human Body Model (Per MIL-STD-883 Method 3015.7) 2000V |

|                                                        |

### **Operating Conditions**

| Temperature Range              | -40 <sup>o</sup> C to 85 <sup>o</sup> C |

|--------------------------------|-----------------------------------------|

| Supply Voltage Range (Typical) | $\pm 4.5V$ to $\pm 15V$                 |

### **Thermal Information**

| Thermal Resistance (Typical, Note 2)                | $\theta_{JA}$ (°C/W)                 |

|-----------------------------------------------------|--------------------------------------|

| PDIP Package                                        | 90                                   |

| SOIC Package                                        | 115                                  |

| Maximum Junction Temperature (Note 1)               |                                      |

| Maximum Junction Temperature (Plastic Package, Note |                                      |

| Maximum Storage Temperature Range                   | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s)            | 300 <sup>0</sup> C                   |

| (SOIC - Lead Tips Only)                             |                                      |

|                                                     |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. Maximum power dissipation, including output load, must be designed to maintain junction temperature below 175°C for die, and below 150°C for plastic packages. See Application Information section for safe operating area information.

- 2.  $\theta_{\text{JA}}$  is measured with the component mounted on an evaluation PC board in free air.

- 3. The non-inverting input of unused amplifiers must be connected to GND.

- 4. Output is protected for short circuits to ground. Brief short circuits to ground will not degrade reliability, however, continuous (100% duty cycle) output current should not exceed 15mA for maximum reliability.

#### **Electrical Specifications** $V_{SUPPLY} = \pm 5V$ , $R_F = 1k\Omega$ , $A_V = +1$ , $R_L = 400\Omega$ , $C_L \le 10pF$ , Unless Otherwise Specified

| PARAMETER                                                      | TEST<br>CONDITIONS                                              | (NOTE 11)<br>TEST<br>LEVEL | TEMP.<br>( <sup>o</sup> C) | MIN  | ТҮР | МАХ  | UNITS              |

|----------------------------------------------------------------|-----------------------------------------------------------------|----------------------------|----------------------------|------|-----|------|--------------------|

| INPUT CHARACTERISTICS                                          |                                                                 |                            |                            |      |     |      |                    |

| Input Offset Voltage (VIO)                                     |                                                                 | A                          | 25                         | -    | 0.8 | 3    | mV                 |

|                                                                |                                                                 | A                          | Full                       | -    | -   | 5    | mV                 |

| Delta V <sub>IO</sub> Between Channels                         |                                                                 | A                          | Full                       | -    | 1.2 | 3.5  | mV                 |

| Average Input Offset Voltage Drift                             |                                                                 | В                          | Full                       | -    | 5   | -    | μV/ <sup>o</sup> C |

| V <sub>IO</sub> Common Mode Rejection Ratio                    | Note 5                                                          | А                          | 25                         | 53   | -   | -    | dB                 |

|                                                                |                                                                 | А                          | Full                       | 50   | -   | -    | dB                 |

| V <sub>IO</sub> Power Supply Rejection Ratio                   | $\pm 3.5 \text{V} \le \text{V}_{\text{S}} \le \pm 6.5 \text{V}$ | А                          | 25                         | 60   | -   | -    | dB                 |

|                                                                |                                                                 | А                          | Full                       | 55   | -   | -    | dB                 |

| Input Common Mode Range                                        | Note 5                                                          | А                          | Full                       | ±2.5 | -   | -    | V                  |

| Non-Inverting Input (+IN) Current                              |                                                                 | А                          | 25                         | -    | 3   | 8    | μΑ                 |

|                                                                |                                                                 | А                          | Full                       | -    | -   | 20   | μΑ                 |

| +IN Common Mode Rejection<br>$(+I_{BCMR} = \frac{1}{+R_{IN}})$ | Note 5                                                          | А                          | 25                         | -    | -   | 0.15 | μΑ/ν               |

|                                                                |                                                                 | А                          | Full                       | -    | -   | 0.5  | μΑ/V               |

| +IN Power Supply Rejection                                     | $\pm 3.5 \text{V} \leq \text{V}_{S} \leq \pm 6.5 \text{V}$      | A                          | 25                         | -    | -   | 0.1  | μΑ/ν               |

|                                                                |                                                                 | А                          | Full                       | -    | -   | 0.3  | μΑ/ν               |

| Inverting Input (-IN) Current                                  |                                                                 | А                          | 25, 85                     | -    | 4   | 12   | μΑ                 |

|                                                                |                                                                 | А                          | -40                        | -    | 10  | 30   | μΑ                 |

| Delta -IN BIAS Current Between                                 |                                                                 | A                          | 25, 85                     | -    | 6   | 15   | μΑ                 |

| Channels                                                       |                                                                 | А                          | -40                        | -    | 10  | 30   | μA                 |

| -IN Common Mode Rejection                                      | Note 5                                                          | A                          | 25                         | -    | -   | 0.4  | μΑ/ν               |

|                                                                |                                                                 | А                          | Full                       | -    | -   | 1.0  | μA/V               |

2

| PARAMETER                              | TEST<br>CONDITIONS                                              | (NOTE 11)<br>TEST<br>LEVEL | TEMP.<br>( <sup>o</sup> C) | MIN   | ТҮР   | МАХ | UNITS              |

|----------------------------------------|-----------------------------------------------------------------|----------------------------|----------------------------|-------|-------|-----|--------------------|

| -IN Power Supply Rejection             | $\pm 3.5 \text{V} \le \text{V}_{\text{S}} \le \pm 6.5 \text{V}$ | А                          | 25                         | -     | -     | 0.2 | μA/V               |

|                                        |                                                                 | А                          | Full                       | -     | -     | 0.5 | μA/V               |

| Input Noise Voltage                    | f = 1kHz                                                        | В                          | 25                         | -     | 4.5   | -   | nV/√ <del>Hz</del> |

| +Input Noise Current                   | f = 1kHz                                                        | В                          | 25                         | -     | 2.5   | -   | pA/√ <del>Hz</del> |

| -Input Noise Current                   | f = 1kHz                                                        | В                          | 25                         | -     | 25.0  | -   | pA/√Hz             |

| TRANSFER CHARACTERISTICS               |                                                                 |                            |                            |       |       |     |                    |

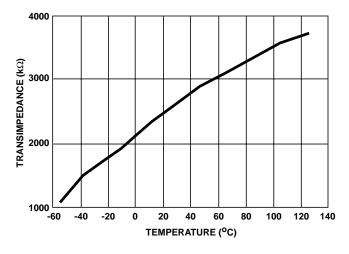

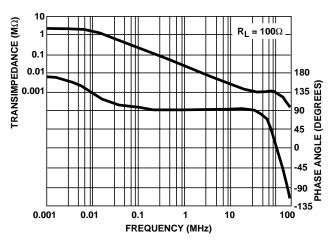

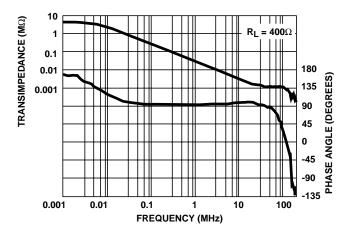

| Transimpedance                         | Note 16                                                         | A                          | 25                         | 1.0   | -     | -   | MΩ                 |

|                                        |                                                                 | А                          | Full                       | 0.85  | -     | -   | MΩ                 |

| Open Loop DC Voltage Gain              | $R_L = 400\Omega$ , $V_{OUT} = \pm 2.5V$                        | A                          | 25                         | 70    | -     | -   | dB                 |

|                                        |                                                                 | А                          | Full                       | 65    | -     | -   | dB                 |

| Open Loop DC Voltage Gain              | $R_L = 100\Omega, V_{OUT} = \pm 2.5V$                           | A                          | 25                         | 50    | -     | -   | dB                 |

|                                        |                                                                 | А                          | Full                       | 45    | -     | -   | dB                 |

| OUTPUT CHARACTERISTICS                 |                                                                 |                            |                            |       |       | •   | ·                  |

| Output Voltage Swing                   | R <sub>L</sub> = 150Ω                                           | A                          | 25                         | ±2.5  | ±3.0  | -   | V                  |

|                                        |                                                                 | А                          | Full                       | ±2.5  | ±3.0  | -   | V                  |

| Output Current                         | R <sub>L</sub> = 150Ω                                           | В                          | Full                       | ±16.6 | ±20.0 | -   | mA                 |

| Output Current, Short Circuit          | $V_{IN} = \pm 2.5 V, V_{OUT} = 0 V$                             | A                          | Full                       | ±40   | ±60   | -   | mA                 |

| Output Current, Disabled               | $\frac{V_{OUT} = \pm 2.5V, V_{IN} = 0V,}{DISABLE = 0V}$         | A                          | Full                       | -     | -     | 2   | μΑ                 |

| Output Disable Time                    | Note 12                                                         | В                          | 25                         | -     | 40    | -   | μs                 |

| Output Enable Time                     | Note 13                                                         | В                          | 25                         | -     | 40    | -   | ns                 |

| Output Capacitance, Disabled           | Note 14                                                         | В                          | 25                         | -     | 15    | -   | pF                 |

| POWER SUPPLY CHARACTERIST              | ICS                                                             |                            |                            |       |       |     |                    |

| Supply Voltage Range                   |                                                                 | А                          | 25                         | 5     | -     | 15  | V                  |

| Quiescent Supply Current               |                                                                 | A                          | Full                       | -     | 7.5   | 10  | mA/Op Amp          |

| Supply Current, Disabled               | DISABLE = 0V                                                    | A                          | Full                       | -     | 5     | 7.5 | mA/Op Amp          |

| Disable Pin Input Current              | DISABLE = 0V                                                    | A                          | Full                       | -     | 1.0   | 1.5 | mA                 |

| Minimum Pin 8 Current to Disable       | Note 6                                                          | A                          | Full                       | 350   | -     | -   | μA                 |

| Maximum Pin 8 Current to Enable        | Note 7                                                          | A                          | Full                       | -     | -     | 20  | μA                 |

| <b>AC CHARACTERISTICS</b> $(A_V = +1)$ |                                                                 | 1                          |                            |       |       | I   |                    |

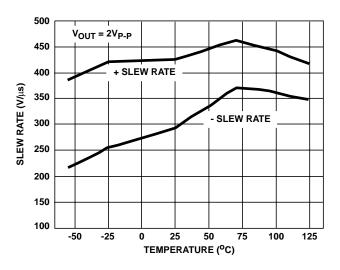

| Slew Rate                              | Note 8                                                          | В                          | 25                         | 275   | 400   | -   | V/µs               |

| Full Power Bandwidth                   | Note 9                                                          | В                          | 25                         | 22    | 28    | -   | MHz                |

| Rise Time                              | Note 10                                                         | В                          | 25                         | -     | 6     | -   | ns                 |

| Fall Time                              | Note 10                                                         | В                          | 25                         | -     | 6     | -   | ns                 |

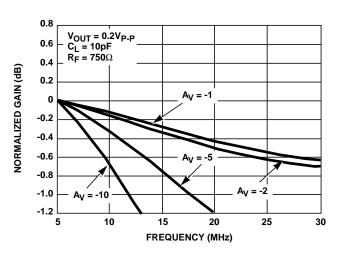

| Propagation Delay                      | Note 10                                                         | В                          | 25                         | -     | 6     | -   | ns                 |

| Overshoot                              |                                                                 | В                          | 25                         | -     | 4.5   | -   | %                  |

| -3dB Bandwidth                         | V <sub>OUT</sub> = 100mV                                        | В                          | 25                         | -     | 125   | -   | MHz                |

| Settling Time to 1%                    | 2V Output Step                                                  | В                          | 25                         | -     | 50    | -   | ns                 |

| Settling Time to 0.25%                 | 2V Output Step                                                  | В                          | 25                         | -     | 75    | -   | ns                 |

## **Electrical Specifications** $V_{SUPPLY} = \pm 5V$ , $R_F = 1k\Omega$ , $A_V = +1$ , $R_L = 400\Omega$ , $C_L \le 10pF$ , Unless Otherwise Specified (Continued)

3

| PARAMETER                              | TEST<br>CONDITIONS          | (NOTE 11)<br>TEST<br>LEVEL | TEMP.<br>( <sup>o</sup> C) | MIN | ТҮР  | МАХ | UNITS   |

|----------------------------------------|-----------------------------|----------------------------|----------------------------|-----|------|-----|---------|

| AC CHARACTERISTICS ( $A_V = 4$         | -2, R <sub>F</sub> = 681Ω)  |                            |                            |     |      |     |         |

| Slew Rate                              | Note 8                      | В                          | 25                         | -   | 475  | -   | V/µs    |

| Full Power Bandwidth                   | Note 9                      | В                          | 25                         | -   | 26   | -   | MHz     |

| Rise Time                              | Note 10                     | В                          | 25                         | -   | 6    | -   | ns      |

| Fall Time                              | Note 10                     | В                          | 25                         | -   | 6    | -   | ns      |

| Propagation Delay                      | Note 10                     | В                          | 25                         | -   | 6    | -   | ns      |

| Overshoot                              |                             | В                          | 25                         | -   | 12   | -   | %       |

| -3dB Bandwidth                         | V <sub>OUT</sub> = 100mV    | В                          | 25                         | -   | 95   | -   | MHz     |

| Settling Time to 1%                    | 2V Output Step              | В                          | 25                         | -   | 50   | -   | ns      |

| Settling Time to 0.25%                 | 2V Output Step              | В                          | 25                         | -   | 100  | -   | ns      |

| Gain Flatness                          | 5MHz                        | В                          | 25                         | -   | 0.02 | -   | dB      |

|                                        | 20MHz                       | В                          | 25                         | -   | 0.07 | -   | dB      |

| AC CHARACTERISTICS (A <sub>V</sub> = + | -10, R <sub>F</sub> = 383Ω) | I                          |                            | 1   |      | 1   | 1       |

| Slew Rate                              | Note 8                      | В                          | 25                         | 350 | 475  | -   | V/µs    |

| Full Power Bandwidth                   | Note 9                      | В                          | 25                         | 28  | 38   | -   | MHz     |

| Rise Time                              | Note 10                     | В                          | 25                         | -   | 8    | -   | ns      |

| Fall Time                              | Note 10                     | В                          | 25                         | -   | 9    | -   | ns      |

| Propagation Delay                      | Note 10                     | В                          | 25                         | -   | 9    | -   | ns      |

| Overshoot                              |                             | В                          | 25                         | -   | 1.8  | -   | %       |

| -3dB Bandwidth                         | V <sub>OUT</sub> = 100mV    | В                          | 25                         | -   | 65   | -   | MHz     |

| Settling Time to 1%                    | 2V Output Step              | В                          | 25                         | -   | 75   | -   | ns      |

| Settling Time to 0.1%                  | 2V Output Step              | В                          | 25                         | -   | 130  | -   | ns      |

| VIDEO CHARACTERISTICS                  | 1                           | I                          |                            | 1   | 1    | 1   |         |

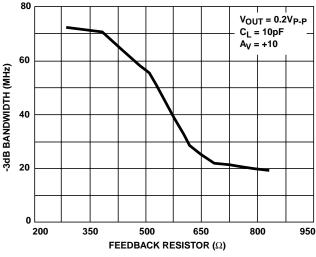

| Differential Gain (Note 15)            | R <sub>L</sub> = 150Ω       | В                          | 25                         | -   | 0.03 | -   | %       |

| Differential Phase (Note 15)           | R <sub>L</sub> = 150Ω       | В                          | 25                         | -   | 0.03 | -   | Degrees |

| <b>Electrical Specifications</b> $V_{SUPPLY} = \pm 5V$ , $R_F = 1k\Omega$ , $A_V = +1$ , $R_L =$ | $= 400\Omega, C_1 \leq 10pF$ , Unless Otherwise Specified (Continued) | d) |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----|

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----|

NOTES:

5.  $V_{CM} = \pm 2.5V$ . At -40<sup>o</sup>C Product is tested at  $V_{CM} = \pm 2.25V$  because short test duration does not allow self heating.

6.  $R_L = 100\Omega$ ,  $V_{IN} = 2.5V$ . This is the minimum current which must be pulled out of the Disable pin in order to disable the output. The output is considered disabled when -10mV  $\leq V_{OUT} \leq$  +10mV.

7. V<sub>IN</sub> = 0V. This is the maximum current that can be pulled out of the Disable pin with the HA5022 remaining enabled. The HA5022 is considered disabled when the supply current has decreased by at least 0.5mA.

8. V<sub>OUT</sub> switches from -2V to +2V, or from +2V to -2V. Specification is from the 25% to 75% points.

9. FPBW =  $\frac{\text{Slew Rate}}{2\pi V_{\text{PEAK}}}$ ;  $V_{\text{PEAK}} = 2V$ .

10.  $R_L = 100\Omega$ ,  $V_{OUT} = 1V$ . Measured from 10% to 90% points for rise/fall times; from 50% points of input and output for propagation delay.

11. A. Production Tested; B. Typical or Guaranteed Limit based on characterization; C. Design Typical for information only.

12.  $V_{IN} = +2V$ , DISABLE = +5V to 0V. Measured from the 50% point of DISABLE to  $V_{OUT} = 0V$ .

13.  $V_{IN} = +2V$ , DISABLE = 0V to +5V. Measured from the 50% point of DISABLE to  $V_{OUT} = 2V$ .

14.  $V_{IN} = 0V$ , Force  $V_{OUT}$  from 0V to ±2.5V,  $t_R = t_F = 50$ ns,  $\overline{DISABLE} = 0V$ .

15. Measured with a VM700A video tester using an NTC-7 composite VITS.

16. V<sub>OUT</sub> = ±2.5V. At -40°C Product is tested at V<sub>OUT</sub> = ±2.25V because short test duration does not allow self heating.

# Test Circuits and Waveforms

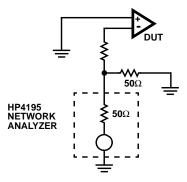

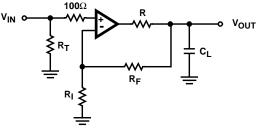

FIGURE 1. TEST CIRCUIT FOR TRANSIMPEDANCE MEASUREMENTS

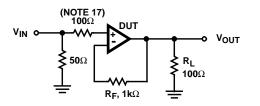

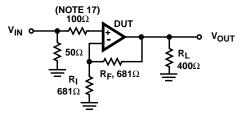

FIGURE 2. SMALL SIGNAL PULSE RESPONSE CIRCUIT

NOTE:

17. A series input resistor of  $\geq 100\Omega$  is recommended to limit input currents in case input signals are present before the HA5022 is powered up.

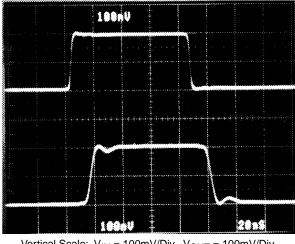

Vertical Scale:  $V_{IN} = 100 \text{mV/Div.}$ ,  $V_{OUT} = 100 \text{mV/Div.}$ Horizontal Scale: 20ns/Div.

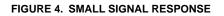

FIGURE 5. LARGE SIGNAL RESPONSE

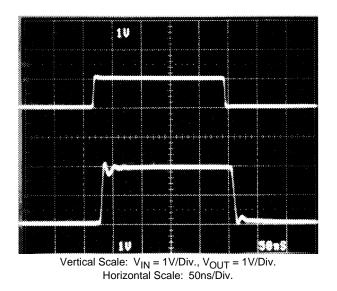

# Schematic Diagram (One Amplifier of Two)

HA5022

0

intersil

# Application Information

## **Optimum Feedback Resistor**

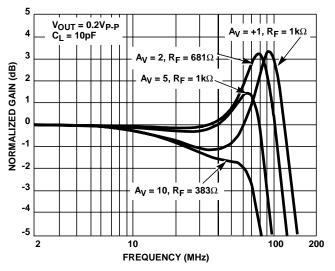

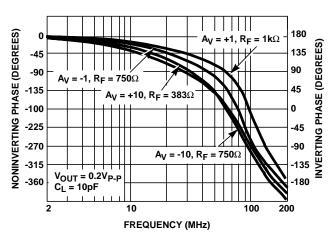

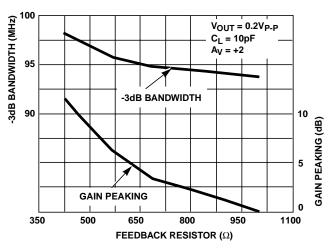

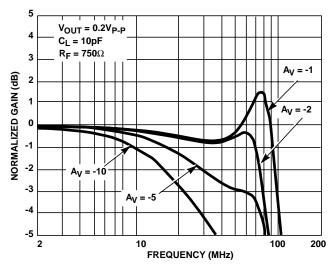

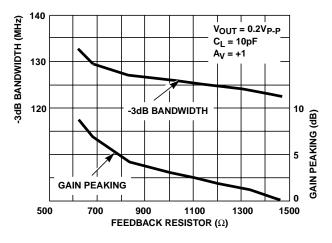

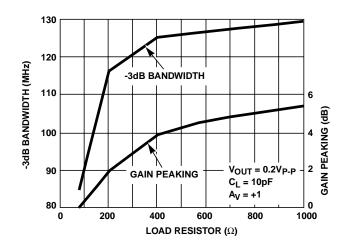

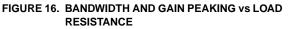

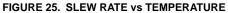

The plots of inverting and non-inverting frequency response, see Figure 11 and Figure 12 in the Typical Performance Curves section, illustrate the performance of the HA5022 in various closed loop gain configurations. Although the bandwidth dependency on closed loop gain isn't as severe as that of a voltage feedback amplifier, there can be an appreciable decrease in bandwidth at higher gains. This decrease may be minimized by taking advantage of the current feedback amplifier's unique relationship between bandwidth and R<sub>F</sub>. All current feedback amplifiers require a feedback resistor, even for unity gain applications, and R<sub>F</sub>, in conjunction with the internal compensation capacitor, sets the dominant pole of the frequency response. Thus, the amplifier's bandwidth is inversely proportional to RF. The HA5022 design is optimized for a  $1000\Omega$  R<sub>F</sub> at a gain of +1. Decreasing R<sub>F</sub> in a unity gain application decreases stability, resulting in excessive peaking and overshoot. At higher gains the amplifier is more stable, so R<sub>F</sub> can be decreased in a trade-off of stability for bandwidth.

The table below lists recommended  $\mathsf{R}_\mathsf{F}$  values for various gains, and the expected bandwidth.

| GAIN<br>(A <sub>CL</sub> ) | <b>R<sub>F</sub> (</b> Ω) | BANDWIDTH<br>(MHz) |

|----------------------------|---------------------------|--------------------|

| -1                         | 750                       | 100                |

| +1                         | 1000                      | 125                |

| +2                         | 681                       | 95                 |

| +5                         | 1000                      | 52                 |

| +10                        | 383                       | 65                 |

| -10                        | 750                       | 22                 |

# PC Board Layout

The frequency response of this amplifier depends greatly on the amount of care taken in designing the PC board. The use of low inductance components such as chip resistors and chip capacitors is strongly recommended. If leaded components are used the leads must be kept short especially for the power supply decoupling components and those components connected to the inverting input.

Attention must be given to decoupling the power supplies. A large value ( $10\mu F$ ) tantalum or electrolytic capacitor in parallel with a small value ( $0.1\mu F$ ) chip capacitor works well in most cases.

A ground plane is strongly recommended to control noise. Care must also be taken to minimize the capacitance to ground seen by the amplifier's inverting input (-IN). The larger this capacitance, the worse the gain peaking, resulting in pulse overshoot and possible instability. It is recommended that the ground plane be removed under traces connected to -IN, and that connections to -IN be kept

7

as short as possible to minimize the capacitance from this node to ground.

# Driving Capacitive Loads

Capacitive loads will degrade the amplifier's phase margin resulting in frequency response peaking and possible oscillations. In most cases the oscillation can be avoided by placing an isolation resistor (R) in series with the output as shown in Figure 6.

FIGURE 6. PLACEMENT OF THE OUTPUT ISOLATION RESISTOR, R

The selection criteria for the isolation resistor is highly dependent on the load, but  $27\Omega$  has been determined to be a good starting value.

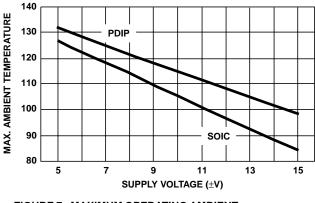

# Power Dissipation Considerations

Due to the high supply current inherent in dual amplifiers, care must be taken to insure that the maximum junction temperature (T<sub>J</sub>, see Absolute Maximum Ratings) is not exceeded. Figure 7 shows the maximum ambient temperature versus supply voltage for the available package styles (PDIP, SOIC). At V<sub>S</sub> = ±5V quiescent operation both package styles may be operated over the full industrial range of -40°C to 85°C. It is recommended that thermal calculations, which take into account output power, be performed by the designer.

FIGURE 7. MAXIMUM OPERATING AMBIENT TEMPERATURE vs SUPPLY VOLTAGE

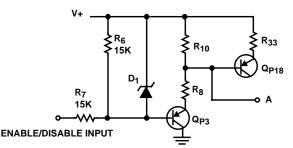

# Enable/Disable Function

When enabled the amplifier functions as a normal current feedback amplifier with all of the data in the electrical specifications table being valid and applicable. When disabled the amplifier output assumes a true high impedance state and the supply current is reduced significantly.

The circuit shown in Figure 8 is a simplified schematic of the enable/disable function. The large value resistors in series with the DISABLE pin makes it appear as a current source to the driver. When the driver pulls this pin low current flows out of the pin and into the driver. This current, which may be as large as  $350\mu$ A when external circuit and process variables are at their extremes, is required to insure that point "A" achieves the proper potential to disable the output. The driver must have the compliance and capability of sinking all of this current.

FIGURE 8. SIMPLIFIED SCHEMATIC OF ENABLE/DISABLE FUNCTION

When V<sub>CC</sub> is +5V the DISABLE pin may be driven with a dedicated TTL gate. The maximum low level output voltage of the TTL gate, 0.4V, has enough compliance to insure that the amplifier will always be disabled even though D<sub>1</sub> will not turn on, and the TTL gate will sink enough current to keep point "A" at its proper voltage. When V<sub>CC</sub> is greater than +5V the DISABLE pin should be driven with an open collector device that has a breakdown rating greater than V<sub>CC</sub>.

Referring to Figure 8, it can be seen that  $R_6$  will act as a pullup resistor to +V<sub>CC</sub> if the DISABLE pin is left open. In those cases where the enable/disable function is not required on all circuits some circuits can be permanently enabled by letting the DISABLE pin float. If a driver is used to set the enable/disable level, be sure that the driver does not sink more than 20µA when the DISABLE pin is at a high level. TTL gates, especially CMOS versions, do not violate this criteria so it is permissible to control the enable/disable function with TTL.

# **Typical Applications**

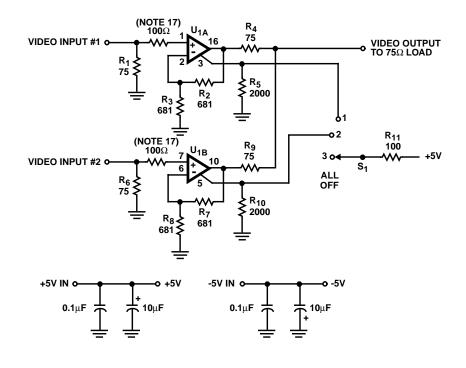

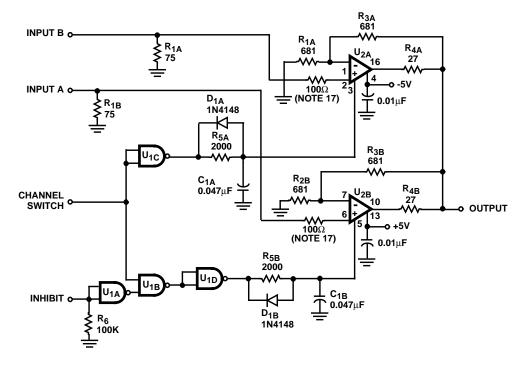

## Two Channel Video Multiplexer

Referring to the amplifier  $U_{1A}$  in Figure 9,  $R_1$  terminates the cable in its characteristic impedance of 75 $\Omega$ , and  $R_4$  back terminates the cable in its characteristic impedance. The amplifier is set up in a gain configuration of +2 to yield an overall network gain of +1 when driving a double terminated cable. The value of  $R_3$  can be changed if a different network gain is desired.  $R_5$  holds the disable pin at ground thus inhibiting the amplifier until the switch,  $S_1$ , is thrown to

position 1. At position 1 the switch pulls the disable pin up to the plus supply rail thereby enabling the amplifier. Since all of the actual signal switching takes place within the amplifier, it's differential gain and phase parameters, which are 0.03% and 0.03 degrees respectively, determine the circuit's performance. The other circuit,  $U_{1B}$ , operates in a similar manner.

When the plus supply rail is 5V the disable pin can be driven by a dedicated TTL gate as discussed earlier. If a multiplexer IC or its equivalent is used to select channels its logic must be break before make. When these conditions are satisfied the HA5022 is often used as a remote video multiplexer, and the multiplexer may be extended by adding more amplifier ICs.

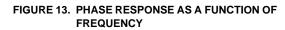

### Low Impedance Multiplexer

Two common problems surface when you try to multiplex multiple high speed signals into a low impedance source such as an A/D converter. The first problem is the low source impedance which tends to make amplifiers oscillate and causes gain errors. The second problem is the multiplexer which supplies no gain, introduces all kinds of distortion and limits the frequency response. Using op amps which have an enable/disable function, such as the HA5022, eliminates the multiplexer problems because the external mux chip is not needed, and the HA5022 can drive low impedance (large capacitance) loads if a series isolation resistor is used.

Referring to Figure 10, both inputs are terminated in their characteristic impedance;  $75\Omega$  is typical for video applications. Since the drivers usually are terminated in their characteristic impedance the input gain is 0.5, thus the amplifiers, U2, are configured in a gain of +2 to set the circuit gain equal to one. Resistors R2 and R3 determine the amplifier gain, and if a different gain is desired R2 should be changed according to the equation  $G = (1 + R_3/R_2)$ . R<sub>3</sub> sets the frequency response of the amplifier so you should refer to the manufacturers data sheet before changing its value. R<sub>5</sub>, C<sub>1</sub> and D<sub>1</sub> are an asymmetrical charge/discharge time circuit which configures U1 as a break before make switch to prevent both amplifiers from being active simultaneously. If this design is extended to more channels the drive logic must be designed to be break before make. R<sub>4</sub> is enclosed in the feedback loop of the amplifier so that the large open loop amplifier gain of U<sub>2</sub> will present the load with a small closed loop output impedance while keeping the amplifier stable for all values of load capacitance.

The circuit shown in Figure 10 was tested for the full range of capacitor values with no oscillations being observed; thus, problem one has been solved. The frequency and gain characteristics of the circuit are now those of the amplifier independent of any multiplexing action; thus, problem two has been solved. The multiplexer transition time is approximately  $15\mu$ s with the component values shown.

NOTES:

- 18. U<sub>1</sub> is HA5022.

- 19. All resistors in  $\Omega$ .

- 20.  $S_1$  is break before make.

- 21. Use ground plane.

#### FIGURE 9. TWO CHANNEL HIGH IMPEDANCE MULTIPLEXER

NOTES:

22. U<sub>2</sub>: HA5022.

23. U<sub>1</sub>: CD4011.

#### FIGURE 10. LOW IMPEDANCE MULTIPLEXER

9

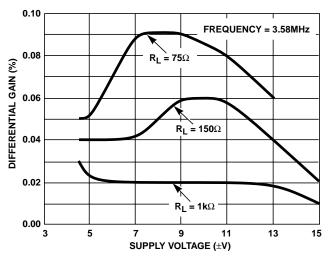

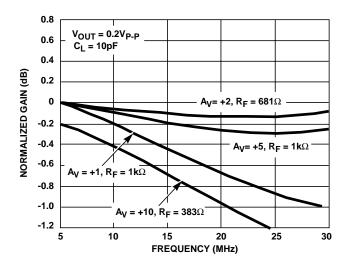

**Typical Performance Curves**  $V_{SUPPLY} = \pm 5V$ ,  $A_V = +1$ ,  $R_F = 1k\Omega$ ,  $R_L = 400\Omega$ ,  $T_A = 25^{\circ}C$ , Unless Otherwise Specified

FIGURE 11. NON-INVERTING FREQUENCY RESPONSE

FIGURE 15. BANDWIDTH AND GAIN PEAKING vs FEEDBACK RESISTANCE

FIGURE 12. INVERTING FREQUENCY RESPONSE

FIGURE 14. BANDWIDTH AND GAIN PEAKING vs FEEDBACK RESISTANCE

$\label{eq:supply} \textit{Typical Performance Curves} \quad \forall_{\text{SUPPLY}} = \pm 5 \forall, \ \text{A}_{V} = +1, \ \text{R}_{F} = 1 \ \text{k} \Omega, \ \text{R}_{L} = 400 \Omega, \ \text{T}_{A} = 25^{o} \text{C}, \ \text{Unless Otherwise Specified} \quad \text{(Continued)} = 10^{\circ} \text{C}, \ \text{Continued} = 10$

FIGURE 17. BANDWIDTH vs FEEDBACK RESISTANCE

FIGURE 19. DIFFERENTIAL GAIN vs SUPPLY VOLTAGE

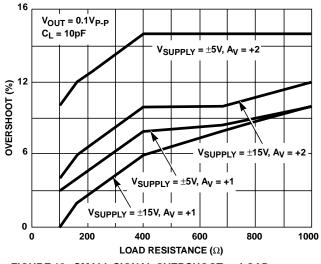

FIGURE 18. SMALL SIGNAL OVERSHOOT vs LOAD RESISTANCE

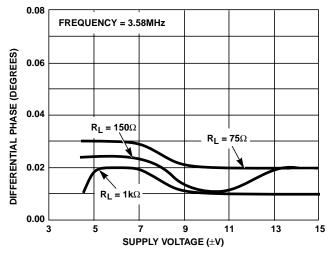

FIGURE 20. DIFFERENTIAL PHASE vs SUPPLY VOLTAGE

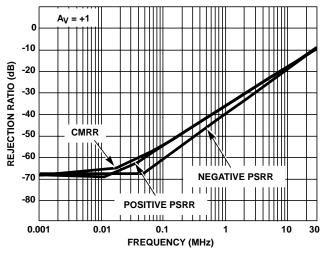

FIGURE 22. REJECTION RATIOS vs FREQUENCY

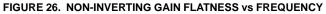

$\textbf{Typical Performance Curves} \quad V_{SUPPLY} = \pm 5 V, \ A_V = +1, \ R_F = 1 k\Omega, \ R_L = 400\Omega, \ T_A = 25^oC, \ Unless \ Otherwise \ Specified \ \textbf{(Continued)}$

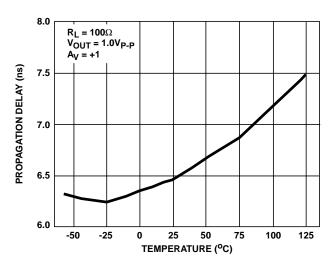

FIGURE 23. PROPAGATION DELAY vs TEMPERATURE

FIGURE 27. INVERTING GAIN FLATNESS vs FREQUENCY

FIGURE 24. PROPAGATION DELAY vs SUPPLY VOLTAGE

FIGURE 28. INPUT NOISE CHARACTERISTICS

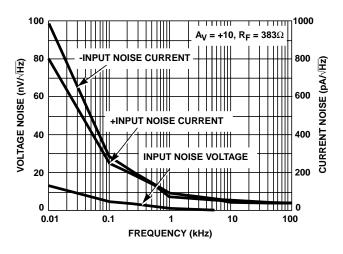

$\label{eq:superior} \textit{Typical Performance Curves} \quad \forall_{\text{SUPPLY}} = \pm 5 \forall, \ \text{A}_{\text{V}} = +1, \ \text{R}_{\text{F}} = 1 \ \text{k} \Omega, \ \text{R}_{\text{L}} = 400 \Omega, \ \text{T}_{\text{A}} = 25^{\text{o}} \text{C}, \ \text{Unless Otherwise Specified} \quad \text{(Continued)} = 10^{10} \ \text{Continued} = 10^{10} \ \text{Con$

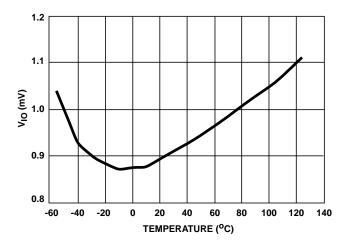

FIGURE 29. INPUT OFFSET VOLTAGE vs TEMPERATURE

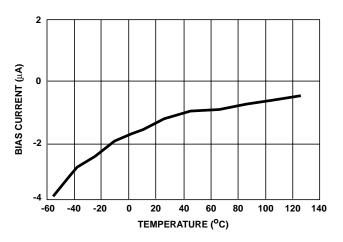

FIGURE 31. -INPUT BIAS CURRENT vs TEMPERATURE

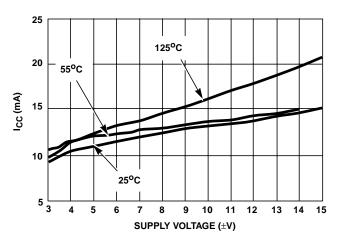

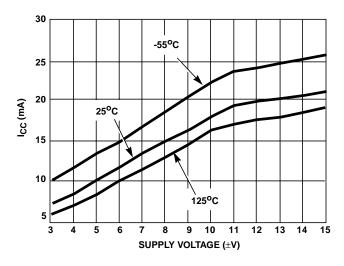

FIGURE 33. SUPPLY CURRENT vs SUPPLY VOLTAGE

13

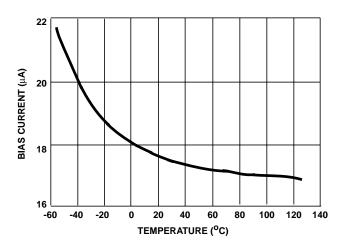

FIGURE 30. +INPUT BIAS CURRENT vs TEMPERATURE

FIGURE 32. TRANSIMPEDANCE vs TEMPERATURE

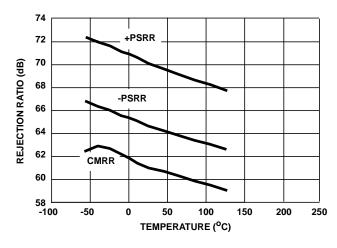

FIGURE 34. REJECTION RATIO vs TEMPERATURE

$\textbf{Typical Performance Curves} \quad \forall_{SUPPLY} = \pm 5 \forall, A_V = +1, R_F = 1 k\Omega, R_L = 400\Omega, T_A = 25^{o}C, \text{ Unless Otherwise Specified} \quad \textbf{(Continued)}$

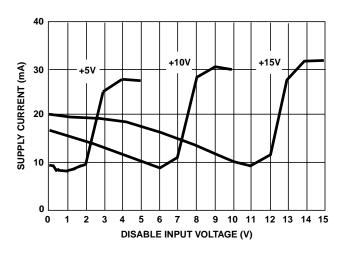

FIGURE 35. SUPPLY CURRENT vs DISABLE INPUT VOLTAGE

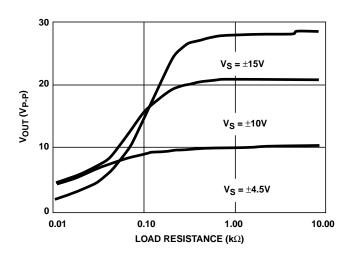

FIGURE 37. OUTPUT SWING vs LOAD RESISTANCE

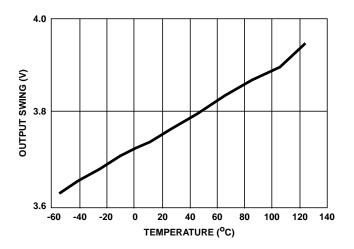

FIGURE 36. OUTPUT SWING vs TEMPERATURE

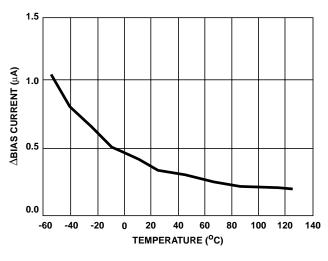

FIGURE 38. INPUT OFFSET VOLTAGE CHANGE BETWEEN CHANNELS vs TEMPERATURE

FIGURE 40. DISABLE SUPPLY CURRENT vs SUPPLY VOLTAGE

$\label{eq:supply} \textit{Typical Performance Curves} \quad \forall_{\text{SUPPLY}} = \pm 5 \forall, \ \text{A}_{\text{V}} = +1, \ \text{R}_{\text{F}} = 1 \ \text{k} \Omega, \ \text{R}_{\text{L}} = 400 \Omega, \ \text{T}_{\text{A}} = 25^{\circ} \text{C}, \ \text{Unless Otherwise Specified} \quad \text{(Continued)} = 10^{\circ} \text{C}, \ \text{Continued} = 10^{\circ} \text{C}, \ \text{Con$

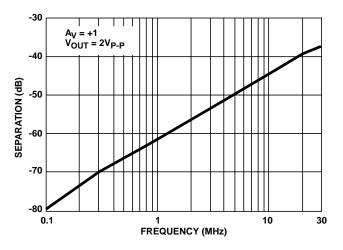

FIGURE 41. CHANNEL SEPARATION vs FREQUENCY

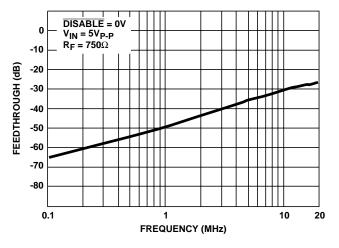

FIGURE 43. DISABLE FEEDTHROUGH vs FREQUENCY

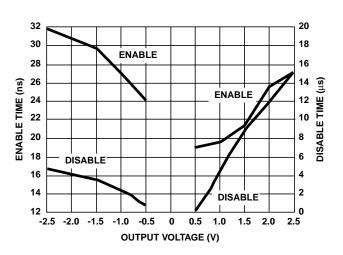

FIGURE 42. ENABLE/DISABLE TIME vs OUTPUT VOLTAGE

FIGURE 44. TRANSIMPEDANCE vs FREQUENCY

15 **intersil**

HA5022

# **Die Characteristics**

### DIE DIMENSIONS:

1650μm x 2540μm x 483μm

#### **METALLIZATION:**

Type: Metal 1: AlCu (1%) Thickness: Metal 1: 8kÅ ±0.4kÅ Type: Metal 2: AlCu (1%) Thickness: Metal 2: 16kÅ ±0.8kÅ

### SUBSTRATE POTENTIAL (POWERED UP):

V-

# Metallization Mask Layout

### PASSIVATION:

Type: Nitride Thickness: 4kÅ ±0.4kÅ

### TRANSISTOR COUNT:

124

### PROCESS:

High Frequency Bipolar Dielectric Isolation

INIOUTINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIINIIN

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com